※本ブログは、SIMULIA Blog (英語版)で既に発表されたブログの日本語参考訳です。

はじめに

半導体業界の根幹をなす有名な「ムーアの法則」は、チップ上のトランジスタ密度が2年ごとに倍増すると予測しています。しかし、近年では、半導体メーカーが物理的な限界に近づき、新技術の開発コストが急速に増加するにつれて、ムーアの法則は減速しています。その代わりに、チップメーカーはチップ性能を向上させるための他の方法を模索しています。

有望なアプローチの一つが、「異種統合(Heterogeneous Integration)」です。モノリシックなシリコンウェハー上にすべての機能を実装する代わりに、異なるチップレットに異なる機能をパッケージ化し、それぞれに最適でコスト効果の高い製造ノードを使用して、それらをシステムオンチップ(SoC)に統合します。モジュール型のチップレットは、アプリケーションのニーズに応じてさまざまな方法で組み合わせることができ、モノリシックなアプローチと比較して、異種集積はコストを削減し、性能の限界を引き続き押し広げることができます。

チップレットを接続するためには、高並列バスインターフェースを使用し、ソースシンクロナスアーキテクチャがよく利用されます。これにより、レイテンシを低減し、高い帯域幅を維持することができます。しかし、この実装には固有の課題もあります。 本ブログでは、エンジニアが最先端のSoCを設計する場合に役立つ、ソースシンクロナスアーキテクチャを用いたチップレット間のインターコネクトのソースシンクロナスアーキテクチャ解析および最適化する方法の概要を説明します。SOC本内容は、2023年のDesignConで発表された論文を基にしており、SIMULIAコミュニティで全文を読むことができます。(SIMULIA Community)

チップレットアーキテクチャの課題

異種統合で設計されたSOCSoCの分散型構造を持ち、すべてのチップレットが接続される必要があります。しかし、この接続のレイテンシが高すぎると、性能上のメリットが失われてしまいます。

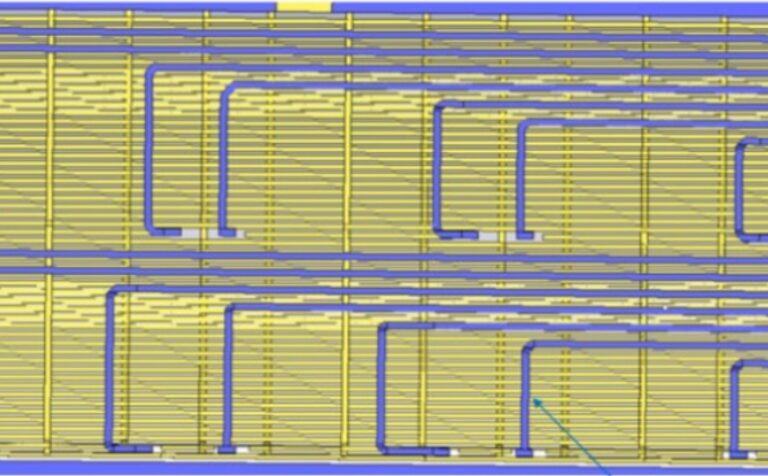

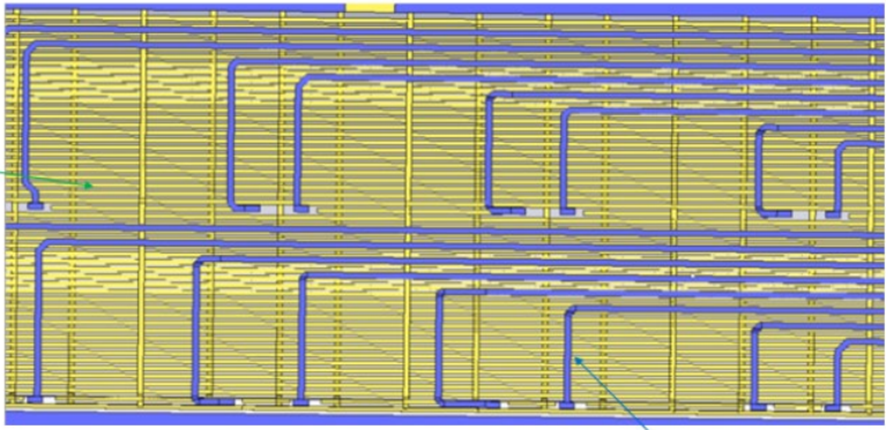

低い送信レイテンシを実現するために、例えば、HBMやUCIeの標準で見られるように、ソースシンクロナスアーキテクチャを備えた並列バスソースシンクロナスアーキテクチャソースシンクロナスアーキテクチャが一般的に使用されます。ソースシンクロナスアーキテクチャでは、クロック(ストローブ)がデータと一緒に専用のトレースで送信されます。異なるトレース間でフライトタイムがにばらつきが生じるため、ストローブによってすべてのデータ信号を正しくサンプリングするためには、データ信号を位相をずらして整合させる必要があります。つまりスキュー(位相のずれ)を揃える必要があります。

データとストローブのトレースのスキューを一致させる必要があることは、チップレットチャネルの実装において非常に重要です。この位相関係を維持するためには、データとストローブをその伝搬遅延に基づいて可能な限り一致させる必要があります。

ソースシンクロナスアーキテクチャの3Dフルウェーブシミュレーション

従来の2D回路抽出シミュレーション手法では、高密度に詰め込まれたチャネル間の高密度の垂直結合や導体の厚さ、抵抗率の影響を捉えることができないため、SoCに対して正確な結果を提供することができません。データレートがGHz単位で測定される場合、非常にわずかなタイミングの不一致でもエラーを引き起こす可能性があるため、これはより大きな問題となります。

シリコンインターポーザーやシリコン貫通ビア(TSV)、メッシュ状のグラウンドプレーンなどの3D構造も考慮する必要があります。シリコンインターポーザーでは、技術規則の要件により、メッシュ状のグラウンドプレーンを使用することが義務付けられています。つまり、2つの信号トレースが同じ長さであっても、リターン電流は異なるルートをたどる可能性があり、その結果、フライトタイムが大きく異なることがあります。

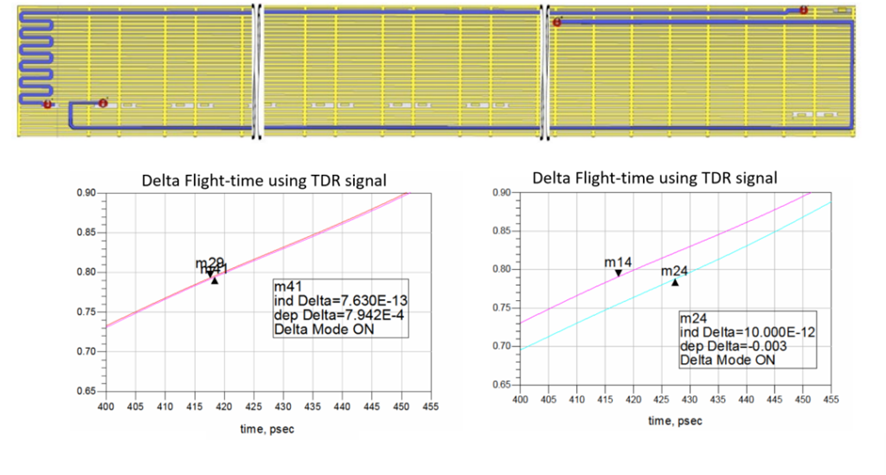

2Dと3Dシミュレーションの比較

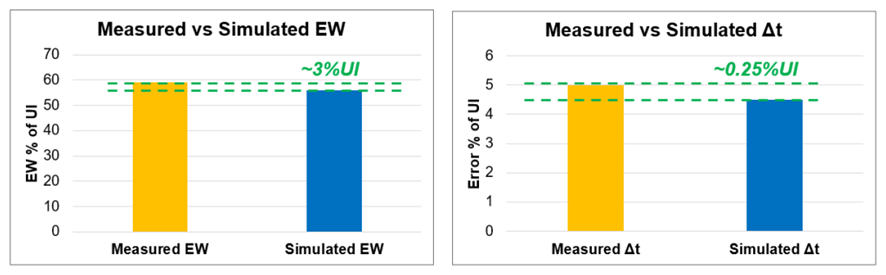

図2のシミュレーションでは、2Dシミュレーションと3Dシミュレーションの選択による影響を示しています。同じ構造で、2Dシミュレーションでは1ps未満の遅延スキューが推定されましたが、3Dシミュレーションでは10psの遅延スキューが計算されました。2Dシミュレーションでは回路構造からの重要な寄与を見逃され、その結果として遅延スキューが10倍に増加しました。10Gbpsのデータチャネルでは、これが10%のエラーレートに相当します。したがって、正確なシミュレーションは非常に重要です。SIMULIA CST Studio Suiteを使用した3Dシミュレーションでは、シミュレーションと測定との間に優れた一致が得られ、エンジニアはシミュレーションに自信を持つことができます(図3)。

ソースシンクロナスアーキテクチャシミュレーションについてさらに学ぶ

この記事では、SOCのシミュレーションに関する基本的な部分だけを取り上げました。シミュレーションと測定、さらにはソースシンクロナスアーキテクチャ設計の基本を示す完全なワークフローについては、当社の論文「3D EM Full Wave Analysis & Optimization for Source Synchronous Interconnect in Heterogeneous Integration Architecture」をご覧ください。この論文はDesignCon 2023で発表され、 SIMULIA Communityで読むことができます。

この記事は、信号品質( SI)および電磁両立性(EMC)の技術者であり、25年以上にわたる高速デジタルおよびアナログインターコネクト(メモリ、イーサネットバックプレーン、PCI-e、DVI/HDMI/LVDS/DP、USB)の設計と分析の経験を持つDr. Hany Fahmyによって執筆されました。HanyはNvidiaでSI/PI/EMCグループのディレクターとしてスマートフォンやタブレット、GPUカードの設計を担当し、高速デジタルソリューションのシミュレーション、モデリング、実験室での特性評価を行っていました。Intel Corporationではメモリアーキテクチャグループのリーダーとして、デスクトップ、モバイル、サーバープラットフォームの設計を担当し、複雑なCPU/GPUおよびチップセットのための設計に従事しました。HanyはDDR1/2/3技術の開発において、Intelを代表してJEDECでメモリアーキテクトを務めました。また、Micron、Agilent Technologies、Texas Instruments Inc.でも勤務経験があります。Hanyは11件の特許を保有しており、現在はIntelligent Solutions BVBAのCEO兼最高顧問として指導しています。また、AMDのシステムIOプラットフォームチームのコンサルタントも務めています。

最新のシミュレーショ ンソリューションにご興味がおありですか?アドバイスやベストプラクティスをお探しですか?他のSIMULIAユーザーやダッソー・システムズの専門家とシミュレーションについてお話しする必要がありますか? SIMULIA Community では、SIMULIA ソフトウェアの最新リソースを検索し、他のユーザーとコミュニケーションを図るためのオンラインコミュニティーです。革新的な思考と知識構築の扉を開く鍵である SIMULIA Communityは、いつでもどこでも知識を広げるために必要なツールを提供します。