안녕하세요. 다쏘시스템코리아 SIMULIA 브랜드팀입니다.

이번 포스팅에서는 CST (Computer Simulation Technology)의 CST PCB STUDIO® (CST PCBS)에 대해 알아보도록 하겠습니다.

CST PCB STUDIO®

CST PCB STUDIO®는 PCB 전용 전자기장 해석 소프트웨어로써 전자장치의 신호 고속화와 소형화로 인해 빈번하게 발생되는 PCB의 신호 무결성 (SI, Signal Integrity)과 전원 무결성 (PI, Power Integrity) 문제를 매우 빠르고, 정확하게 분석할 수 있습니다.

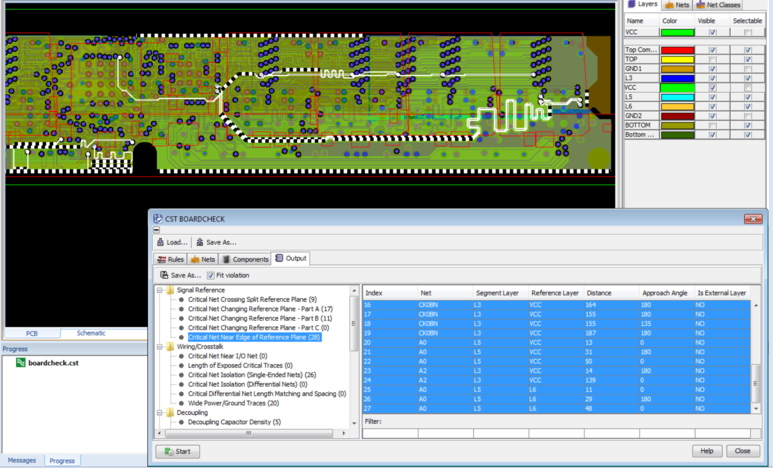

CST PCB STUDIO®는 설계 초기 단계에서 PCB 구조에 대한 Design Rule Checking을 진행할 수 있는 CST BOARDCHECK®과 신호 무결성과 전원 무결성을 분석할 수 있는 각각의 Solver (SI-TD Analysis Solver, SI-FD Analysis Solver, IR-Drop Analysis Solver, PI-FD Analysis Solver), 디커플링 커패시터 배치에 대한 최적화를 진행할 수 있는 De-Cap Optimization Tool로 구성되어 있습니다. 뿐만 아니라, 한 번의 버튼 선택으로 고주파 대역의 전자기장 해석 툴인 CST MICROWAVE STUDIO®에서 사용할 수 있는 3D 모델로 변환할 수 있기 때문에 변환된 3D PCB 데이터와 3D CAD 데이터, 케이블, 회로 등을 하나의 Full 3D 시스템으로 구성하여 EMI/EMC 해석을 매우 편리하게 진행해 볼 수 있습니다.

그림 1. CST BOARDCHECK®을 사용한 PCB Design Rule Checking

CST PCB STUDIO®– Signal Integrity Analysis Solver (SI-TD, SI-FD)

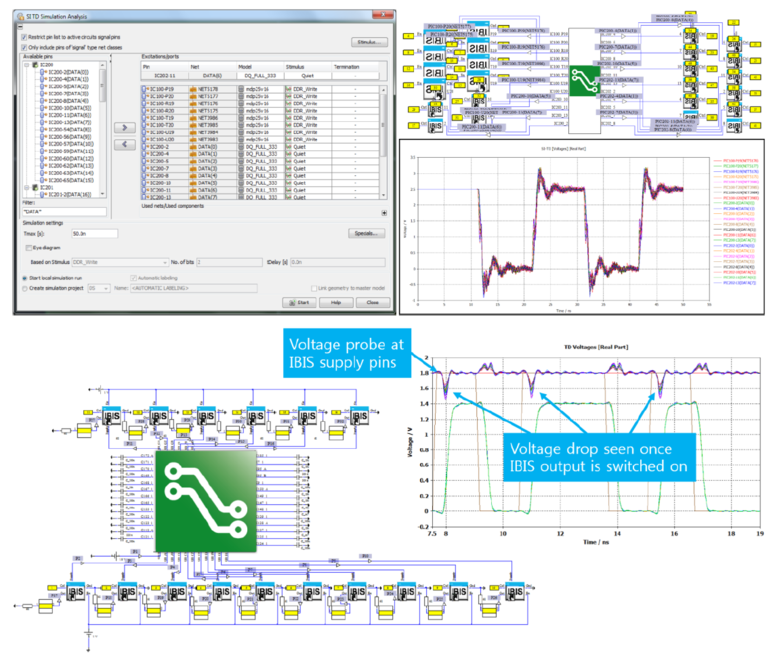

SI-TD Analysis Solver와 SI-FD Analysis Solver는 고속화된 신호를 사용하는 PCB 상에서 요구되는 신호 무결성 설계를 위해 사용할 수 있습니다. 시간 영역을 해석하는 SI-TD Analysis Solver의 경우에는 전송 및 반사되는 신호, 크로스톡, 시간 지연, Eye-Diagram, TDR, SSN/SSO 등에 대한 분석을 진행해 볼 수 있으며, 주파수 영역을 해석하는 SI-FD Analysis Solver의 경우에는 S-Parameter 및 Z-Parameter, SPICE 모델 추출 등에 대한 분석을 진행할 수 있습니다.

그림 2. SI-TD Analysis Solver를 사용한 SSN/SSO 분석

CST PCB STUDIO®– Power Integrity Analysis Solver (IR-Drop, PI-FD)

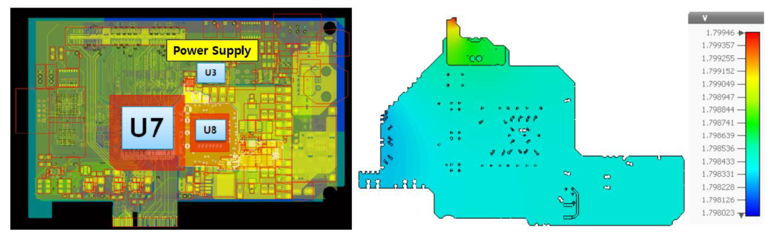

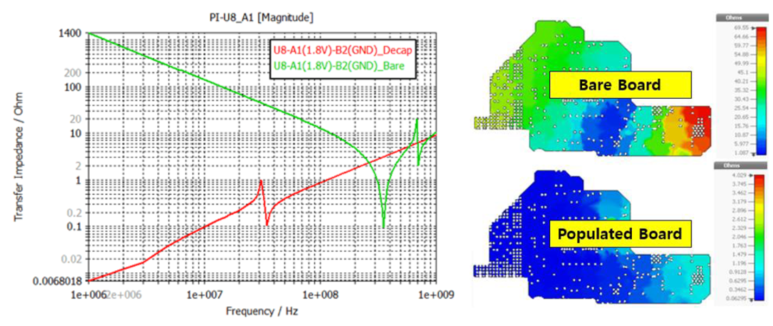

IR-Drop Analysis Solver와 PI-FD Analysis Solver는 높은 임피던스를 갖는 PDN상에 요구되는 전원 무결성 설계를 위해 사용할 수 있습니다. DC 영역에서는 IR-Drop Analysis Solver를 사용하여 파워 서플라이로부터 전원이 공급될 경우에 대한 각 컴포넌트 상에서의 전류 밀도, 표면 전류 밀도, 전압, 전압 강하 등의 결과를 확인할 수 있으며, AC 영역에서는 PI-FD Analysis Solver를 사용하여 주파수 영역에서의 임피던스 레벨을 확인해볼 수 있습니다. 뿐만 아니라 임피던스가 높은 지역에 대해서는 디커플링 커패시터를 직접 위치시킬 수 있기 때문에 매우 효율적인 전원 무결성 설계를 진행해볼 수 있습니다.

그림 3. IR-Drop Analysis Solver를 사용한 전압 강하 분석

그림 4. PI-FD Analysis Solver를 사용한 임피던스 분석

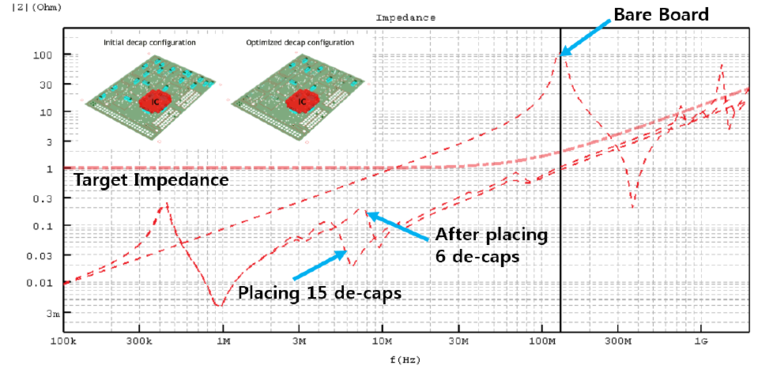

CST PCB STUDIO®– De-Cap Optimization Tool

De-Cap Optimization Tool은 전원 무결성 설계를 위해 사용되는 디커플링 커패시터의 배치에 대한 최적화를 위해 사용할 수 있습니다. 일반적으로 PDN의 높은 임피던스를 저감하기 위해 주로 파워 넷과 그라운드 넷 사이에 디커플링 커패시터를 위치시키게 되는데 CST PCB STUDIO® 내에 있는 De-Cap Optimization Tool을 사용한다면, 사용자가 설정한 타겟 임피던스 레벨 이하로 임피던스를 낮추면서 디커플링 커패시터 수를 최소화 시켜주기 때문에 디커플링 커패시터 배치로 인해 발생되는 비용과 PCB Artwork 상의 복잡성을 줄여줄 수 있습니다.

그림 5. De-Cap Optimization Tool을 사용한 디커플링 커패시터 배치 최적화

위의 내용과 관련해 보다 자세한 설명이 필요하시면 SIMULIA.CST.KR.Hotline@3ds.com 으로 연락 주시길 바랍니다.

※ 부록 – 용어 사전

PCB : Printed Circuit Board : 인쇄 회로 기판

EMI : Electromagnetic Interference : 전자파 간섭

EMC : Electromagnetic Compatibility : 전자파 적합성

TDR : Time Domain Reflectometry : 시간 영역 반사법

SSN : Simultaneous Switching Noise : 동시 스위칭 잡음

SSO : Simultaneous Switching Output : 동시 스위칭 출력

PDN : Power Delivery Network : 전원 공급 회로