*以下は、Inova Semiconductors GmbH のアプリケーション エンジニアである Reiner Welzer氏との共著です。Welzer氏はRF およびアナログ信号 PCB のシグナルインテグリティ、パワーインテグリティ及びEMC規格に準拠した設計において 20 年以上の経験を有しています。近年では特に自動車向けの電子回路の ESD 保護に注力しています。

※本ブログは、SIMULIA Blog (英語版)で既に発表されたブログの日本語参考訳です。

結合されたマイクロストリップラインのモデリング

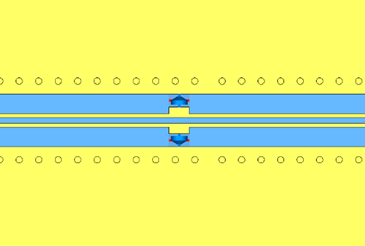

単一ツイストペア ケーブルを介したデータ伝送では、エッジ結合された表面マイクロストリップ導体を使用して PCB 上の接続が実現されます。高速データ伝送には主に差動信号が使用されます。これにより、良好な電磁両立性 (EMC) が実現されます。通常、公称線路インピーダンス 100 Ω のエッジ結合された表面マイクロストリップ導体が使用され、TOP 層に配置されます。図 1 は、シミュレーションに使用されたエッジ結合マイクロストリップラインの寸法を示しており、100 オームの差動ラインインピーダンスを実現します。

線路インピーダンスの計算では、正しい材料特性と正しいソルダーマスク形状のモデリングが重要です。図 1 に示すように、ソルダーマスクのモデリングは、マイクロストリップ導体を覆う薄膜として実現されます。

差動ラインはプラグを介してケーブルに接続されているため、このプラグで ESD事象が発生する可能性が非常に高くなります。このような ESD 事象は、短時間(< 1 ns) で非常に高い電圧と電流のピークを発生させ、電子部品に損傷を与える可能性があります。これを回避するには、差動線路の各導体に ESD 保護部品を接続する必要があります。このような用途には、TVS (過渡電圧抑制) ダイオードがよく使用されます。応答時間が非常に速く、短時間で電圧を一定の値に制限します。

6 Gbps の高速データ レートでは、寄生成分の少ない小型パッケージの部品を使用することが重要です。解析対象のジオメトリには、NEXPERIA の ESD 保護ダイオード PESD5V0C1BLS-Q を使用しました [1]。このデバイスの最大ダイオード容量は 0.3 pF、パッケージサイズは 1 mm x 0.6 mm x 0.47 mm と小型です。シミュレーションでは、ESD ダイオードは「集中定数素子」として定義されます。それらは寄生容量のみを考慮しています。 「集中定数素子」は CST 内部の要素であり、R、L、C コンポーネントで表現できます。図 2 に、ESD ダイオードを含む差動線路のシミュレーションモデルを示します。

図 2 では、差動信号線上の ESD コンポーネントのランディング パッドがトレース幅よりも広いことがわかります。明らかに、この特定の位置での断面積の変化は、線路インピーダンスの変化を引き起こします。このインピーダンス変化のサイズに応じて、信号品質に影響が生じることになります。

レイアウト前 TDR シミュレーション

伝送線路における線路インピーダンスを分析する一般的な手法として、時間領域反射率測定法 (TDR) があります。これは、パルスを送信し、その反射波を入力側で受信するというレーダーの原理と類似しています。反射波を解析することで、線路インピーダンスの特性を把握することができます。 CST Studio Suite は、時間領域ソルバーまたは周波数領域ソルバーを使用して TDR シミュレーションを実行することができます。このレイアウト前の調査では、周波数領域ソルバーを使用します。これは、対象構造の離散化が比較的容易であり、そのサイズが波長に比べて小さいためです。周波数領域ソルバーは S パラメーターの結果のみが得られるため、リターンロスの S パラメーター S11 をポスト処理することで TDR 結果を算出します。入力信号としてガウス信号を定義すると、リターンロス情報から出力信号を再構成できます。式 1 を適用して TDR を計算します。

シミュレーションで定義された最大周波数範囲は 8.4 GHz であり、これは 104 ps の 10% ~ 90% の立ち上がり時間に対応します。

CST Studio Suite では、図 4 に示すように、テンプレートベースのポスト処理「S パラメーターからTDR を計算」を使用して、この計算を自動的に実行できます。

ダイオードの静電容量値はかなり小さい (0.3 pF) ですが、TDR シミュレーションを行う際には考慮する必要があります。この静電容量により、公称線路インピーダンス (100 Ω) が低下します。図 5 は、この静電容量を考慮した場合と考慮しない場合の比較を示しています。

レイアウトの修正

高速データレーンを設計する場合、通常、最大許容インピーダンス変動は ± 10% に設定されます。基準インピーダンスが 100 Ω の場合、図 5 から、曲線は83Ωまで低下します。これは要件の下限 (90 Ω) を満たしません。インピーダンス要件を満たすには、ESD ダイオード周辺のレイアウトを最適化する必要があります。ESD ダイオードの静電容量によりこの領域の線路インピーダンスが低下するため、伝送ラインの 1 メートルあたりの静電容量を減らすことでこの影響を補償する必要があります。これを行う最も効果的な方法は、ESD ダイオードの下の基準面を切り抜くことです。最適な凹みのある基準領域のサイズは、シミュレーションによって求めることができます。図 6 は、シミュレーションを数回繰り返した後、特定の層構成に対して修正された基準面の最適化された構成を示しています。

対応するインピーダンス曲線の改善は、図 7 に示されています。

グランドプレーンの切り抜きにより、他のスイッチング信号や干渉信号との間でクロストークが発生する可能性があることに注意ください。そのため、この切り抜き部分の下には感度の高い信号線を配線しないことをお勧めします。 PCB レイアウト設計ツールでは、制限/禁止領域を作成することで対策できます。

線路インピーダンスの改善は、リターンロスのSパラメーターS11からも確認できます。

(図8) リターンロスは約 12 dB 改善しています。これは、信号品質の向上も意味します。

凹みのある基準面の信号品質が優れていることは、アイダイアグラムの結果を比較することによっても実証できます。使用されるデジタル擬似ランダムビットシーケンス (PRBS) には次の特性があります。

- • PRBS12

- • 差動電圧レベル ± 200 mV

- • 立ち上がりおよび立ち下がり時間は 80 ps、周期長は 3 GHz に対応

図 9 と図 10 は、両方のレイアウトのアイダイアグラムを示しています。

測定値の比較

シミュレーション結果を確認するために、最適化されたパラメーター (CST Studio Suite シミュレーションによって解析された) を使用した PCB レイアウトが作成されています。 TDR インピーダンス測定は、Sequid 社の差動 TDR 測定システムを使用して実施されました。測定中、伝送線路は SMA ソケットを介して接続されました。コネクタは計算能力と時間を増加させるだけであり、ESD ダイオード周囲の線路インピーダンスには影響を与えないため、シミュレーションでは、コネクタを考慮する必要はありません。また、差動線路の端部はオープンのままにすることができます。

測定用に製造された PCB プロトタイプは、4 層で総厚が約 1.6 mm の標準的な FR-4 基板です。差動ペアの寸法は、レイアウト前の検討で使用したものとは若干異なりますが、基準面の切り抜き寸法は同じです。図 11 は、CST Studio Suite による測定比較に使用される PCB レイアウトプロトタイプの断面図を示しています。

測定とシミュレーションの線路インピーダンス結果の比較を図 12 に示します。測定結果との良好な一致により、CST MWS によるシミュレーションの妥当性を確認できます。

結論

高速データ信号を送信するには、高速データ レーン全体の線路インピーダンス曲線を滑らかにすることが重要です。信号品質の要件は通常、基準インピーダンスから±10%です。このブログ記事では、CST Studio Suite を使用して、このような伝送線路の 3D レイアウトシミュレーションと最適化について紹介しました。特に開発期間に関して、レイアウト前の段階でこのシミュレーション ツールを使用する利点を示しました。より現実的な結果を得るためには、最適化中に ESD ダイオード部品(静電容量情報) を考慮することが重要であることを示しました。最後に、シミュレーションと測定結果がよく一致し、CST Studio Suite によるシミュレーション結果の精度が確認されました。

Richard Sjiariel は、2021 年 6 月に Dassault Systemes Deutschland に入社しました。現在は、EMC シミュレーションを主な業務とする SIMULIA インダストリープロセスコンサルタントとして従事しています。 2015 年から 2021 年 5 月まで、ドイツのContinental Automotive GmbH でハードウェア開発者として従事し、自動車用ディスプレイの開発を担当していました。その業務には、電源供給のコンセプト設計、FR4-PCB および Flex-PCB のレイアウト設計、シグナルインテグリティおよびパワーインテグリティのシミュレーション、およびCISPR-25 に準拠した EMC 測定などが含まれます。Continental入社以前には、CST で8年間アプリケーションエンジニアとして勤務し、シグナルインテグリティとパワーインテグリティのアプリケーションに関する技術サポート、トレーニング、ウェビナーを行っていました。2006 年にWuppertal大学で電気工学の修士号を取得しています。

リファレンス

[2] CST Studio Suite 2024 Online Help.

最新のシミュレーショ ンソリューションにご興味がおありですか?アドバイスやベストプラクティスをお探しですか?他のSIMULIAユーザーやダッソー・システムズの専門家とシミュレーションについてお話しする必要がありますか? SIMULIA Community では、SIMULIA ソフトウェアの最新リソースを検索し、他のユーザーとコミュニケーションを図るためのオンラインコミュニティーです。革新的な思考と知識構築の扉を開く鍵である SIMULIA Communityは、いつでもどこでも知識を広げるために必要なツールを提供します。